### Current, Voltage, and Charge Monitor for High Voltage Battery Packs

### FEATURES

- Measures Battery Stack Voltage, Current and Power

- Indicates Accumulated Battery Charge and Energy

- 20-Bit Current Measurement with <1µV Offset</p>

- Built-In Isolated isoSPI<sup>™</sup> or SPI Interface

- LTC68xx/ADBMS68xx Compatible, Supports Synchronous Measurements with Cell Monitors

- Up to 12 Buffered Voltage Measurement Inputs

- Up to 5 GPIOs, Configurable to Drive Ground, Supply or Toggling at 400kHz

- High or Low Side Current Sense

- 0.3% Current and Voltage Accuracy

- 1% Energy and Charge Accuracy

- True Average ADCs

- I<sup>2</sup>C EEPROM Interface to Store Board Calibration Factors

- Threshold Registers for all Measured Quantities

- Engineered for ISO26262 Compliant Systems

- Open Wire Detection on Input Pins

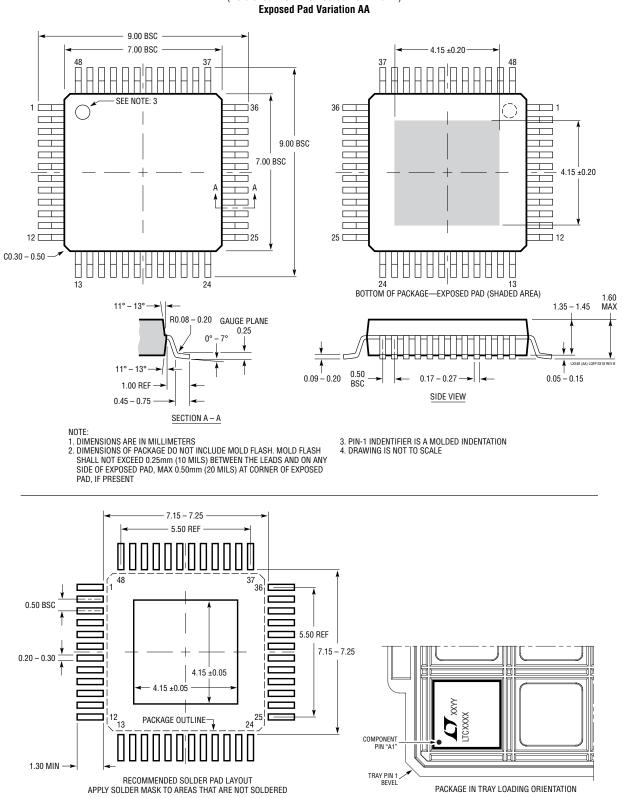

- Available in 48-Lead LQFP Package

- AEC-Q100 Qualified for Automotive Applications

### **APPLICATIONS**

- Electric and Hybrid Vehicles

- Isolated Current Sensing

- Backup Battery Systems

- High Power Portable Equipment

All registered trademarks and trademarks are the property of their respective owners.

# DESCRIPTION

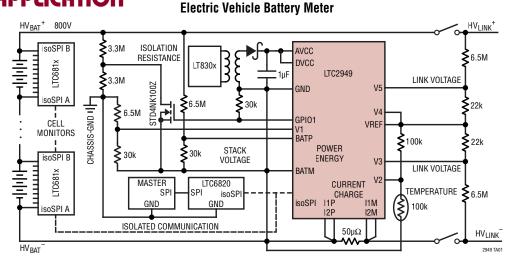

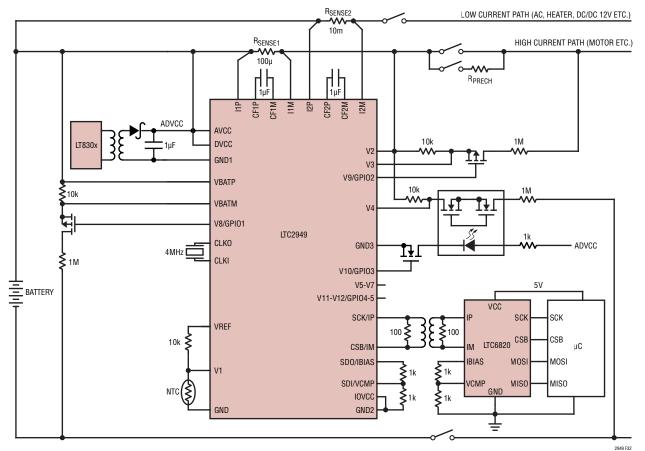

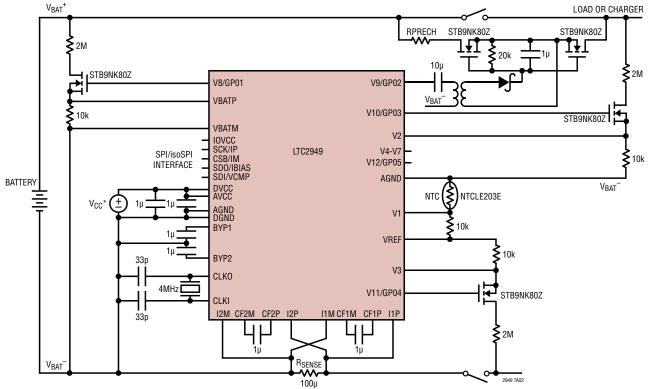

The LTC<sup>®</sup>2949 is a high precision current, voltage, temperature, charge and energy meter for electrical and hybrid vehicles and other isolated current sense applications. It infers charge and energy flowing in and out of the battery pack by monitoring simultaneously the voltage drop over up to two sense resistors and the battery pack voltage.

Low offset  $\Delta\Sigma$  ADCs ensure accurate measurement of voltage and current with insignificant power loss. Continuous integration of current and power ensures lossless tracking of charge and energy delivered or received by the battery pack.

The built-in serial interface can be configured to support isolated isoSPI communication to the host or as SPI interface.

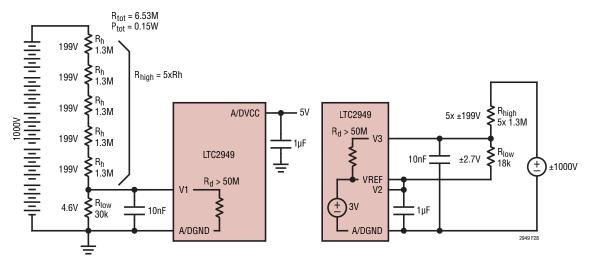

The LTC2949 features 12 internally buffered high impedance inputs (V1 to V12) for measuring voltages from external sensors or resistor dividers allowing to measure temperatures, HV-Link voltages, chassis isolation and supervise contactor states. LTC2949 has up to five programmable digital outputs which can be set to ground, supply or toggling at 400kHz.

Programmable threshold and tracking registers reduce digital traffic to the host.

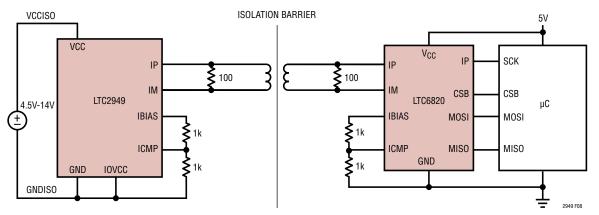

### TYPICAL APPLICATION

# TABLE OF CONTENTS

| Features                                                | 1  |

|---------------------------------------------------------|----|

| Applications                                            | 1  |

| Typical Application                                     | 1  |

| Description                                             | 1  |

| Absolute Maximum Ratings                                | 3  |

| Order Information                                       |    |

| Pin Configuration                                       | 3  |

| Electrical Characteristics                              | 4  |

| Typical Performance Characteristics                     | 10 |

| Pin Functions                                           |    |

| Pin Functions                                           | 12 |

| Block Diagram                                           | 13 |

| Operation                                               |    |

| Overview                                                |    |

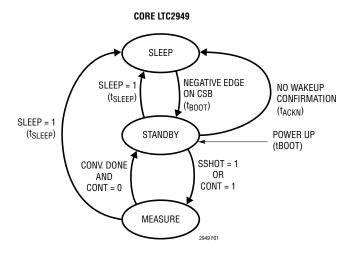

| Modes of Operation                                      | 15 |

| Data Acquisition Channels                               |    |

| Power Measurement                                       |    |

| Charge, Energy and Time                                 | 20 |

| Overcurrent Comparators                                 |    |

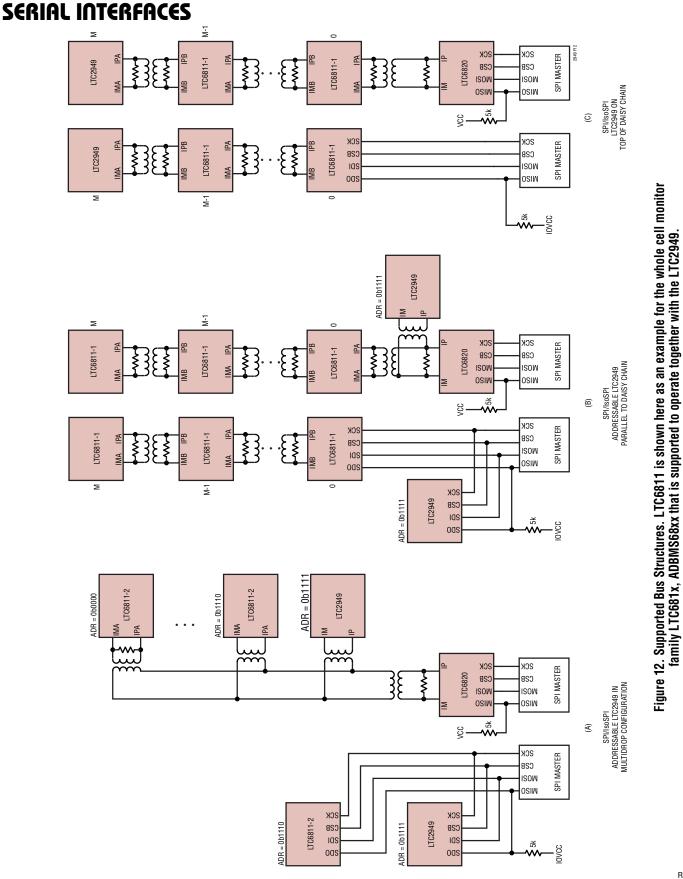

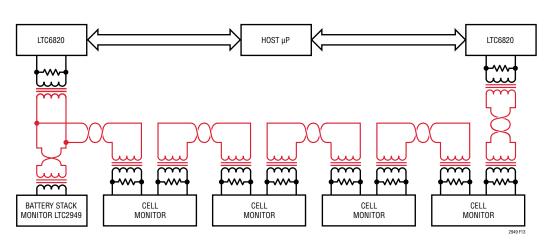

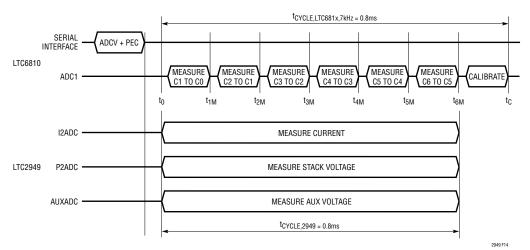

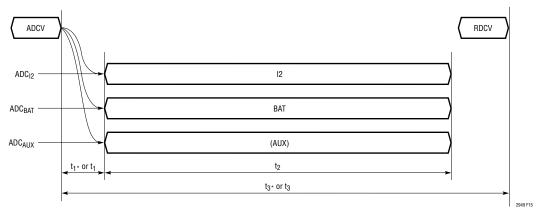

| SERIAL INTERFACES                                       |    |

| Serial Interfaces Overview                              | 22 |

| 4-Wire Serial Peripheral Interface (SPI) Physical Layer | 22 |

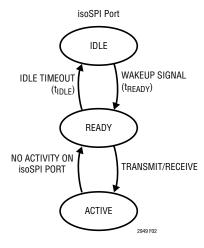

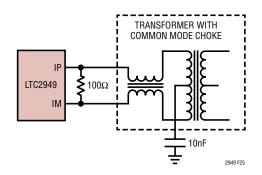

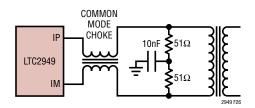

| 2-Wire Isolated Interface (isoSPI) Physical Layer       | 23 |

| Data Link Layer                                         | 28 |

| Network Layer                                           | 28 |

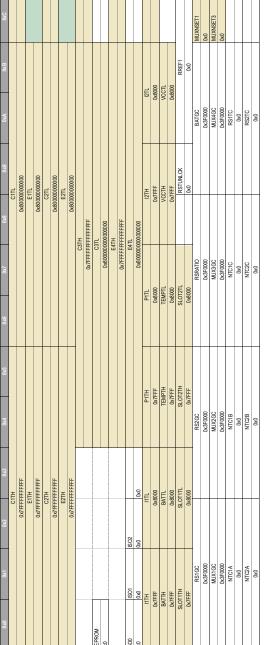

| REGISTER MAP                                            | 41 |

| REGISTER Description                                    | 42 |

| MEMORY MAP AND Paging Mechanism                         | 42 |

| Register Map PAGE0                                      | 44 |

| Register Map PAGE1                                      |    |

| Application Information                                 | 68 |

| Temperature Measurement                                 | 68 |

| Sense Resistor Temperature Compensation                 | 69 |

| Current and Voltage Input Filtering                     |    |

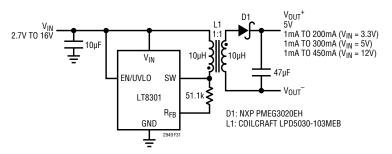

| Powering the LTC2949                                    |    |

| Package Description                                     |    |

| Revision History                                        |    |

| Typical Application                                     |    |

| Related Parts                                           | 80 |

### **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1, 2)

| Supply Pins                             |                                  |

|-----------------------------------------|----------------------------------|

| AVCC to AGND                            | –0.3V to 14.5V                   |

| DVCC to DGND                            | –0.3V to 14.5V                   |

| AVCC to DVCC                            | –0.1V to 0.1V                    |

| DGND to AGND.                           | –0.1V to 0.1V                    |

| Analog Pins                             |                                  |

| I1P, I1M, I2P, I2MC                     | ).3V to V <sub>AVCC</sub> + 0.3V |

| I1P to I1M, I2P to I2M                  | ±1V                              |

| VBATP, VBATMO                           |                                  |

| V1-V12C                                 |                                  |

| CLKO, DNC                               |                                  |

| Digital Input/Output Pins               | . ,                              |

| IOVCC, CLKI, CSB(IM), SCK(IP)           | 0.3V to 5V                       |

| SDI (ICMP), SDO (IBIAS)                 |                                  |

| SDA, SCL                                |                                  |

| Current In/Out of Pins                  |                                  |

| IP, IM                                  | ±30mA                            |

| SDO (IBIAS)                             |                                  |

| V8-V12                                  |                                  |

| VREF (Note 4)                           |                                  |

| BYP1 (Note 4)                           |                                  |

| BYP2 (Note 4)                           |                                  |

| <b>Operating Ambient Temperature Ra</b> |                                  |

| LTC2949I                                | 40°C to 85°C                     |

| LTC2949H                                |                                  |

| Storage Temperature Range               | 65°C to 150°C                    |

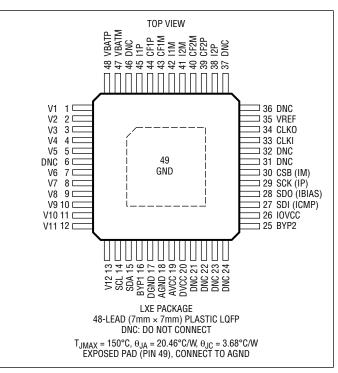

### PIN CONFIGURATION

### **ORDER INFORMATION**

#### AUTOMOTIVE PRODUCTS\*\*

| TRAY (250PC)       | TAPE AND REEL (2000PC) | PART MARKING* | PACKAGE DESCRIPTION   | MSL RATING | TEMPERATURE RANGE |

|--------------------|------------------------|---------------|-----------------------|------------|-------------------|

| LTC2949ILXE#3ZZPBF | LTC2949ILXE#3ZZTRPBF   | LTC2949LXE    | 48-LEAD PLASTIC eLQFP | 3          | -40°C to 85°C     |

| LTC2949HLXE#3ZZPBF | LTC2949HLXE#3ZZTRPBF   | LTC2949LXE    | 48-LEAD PLASTIC eLQFP | 3          | –40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

\*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #3ZZ suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

| SYMBOL            | PARAMETER                                                              | CONDITIONS                                                                                                                                                            |           | Ţ | MIN   | ТҮР                    | MAX                     | UNITS             |

|-------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|-------|------------------------|-------------------------|-------------------|

| Power Sup         | ply                                                                    |                                                                                                                                                                       |           | 1 |       |                        | I                       |                   |

| V <sub>AVCC</sub> | Analog Supply Voltage                                                  |                                                                                                                                                                       |           |   | 4.5   |                        | 14                      | V                 |

| V <sub>DVCC</sub> | Digital Supply Voltage                                                 |                                                                                                                                                                       |           |   | 4.5   |                        | 14                      | V                 |

| V <sub>UVLO</sub> | Supply Undervoltage Lockout Threshold                                  | V <sub>AVCC</sub> , V <sub>DVCC</sub> Falling                                                                                                                         |           |   |       |                        | 4.5                     | V                 |

| Icc               | Average Supply Current into AVCC and DVCC                              | Core State: STANDBY o                                                                                                                                                 | r MEASURE |   |       | 16                     | 20                      | mA                |

|                   |                                                                        | Core State: SLEEP                                                                                                                                                     |           |   |       | 9                      | 15                      | μA                |

|                   |                                                                        | Core State: SLEEP                                                                                                                                                     |           |   |       |                        | 150                     | μA                |

|                   | Additional DVCC Supply Current if isoSPI in                            | $R_{B1} + R_{B2} = 2k$                                                                                                                                                | READY     |   |       | 4.8                    | 5.8                     | mA                |

|                   | READY/ACTIVE States                                                    |                                                                                                                                                                       | ACTIVE    |   |       | 6.1                    | 7.8                     | mA                |

|                   | Note: ACTIVE State Current Assumes t <sub>CLK</sub> = 1µs,<br>(Note 5) | $R_{B1} + R_{B2} = 20k$                                                                                                                                               | READY     |   |       | 2.1                    | 3                       | mA                |

|                   |                                                                        |                                                                                                                                                                       | ACTIVE    |   |       | 2.5                    | 3.5                     | mA                |

| V <sub>BYP1</sub> | BYP1 Regulated Output Voltage                                          |                                                                                                                                                                       | <b>I</b>  |   | 2.25  | 2.5                    | 2.75                    | V                 |

|                   | BYP1 Load Current                                                      |                                                                                                                                                                       |           |   | -10   |                        | 0                       | mA                |

|                   | BYP1 Load Regulation Error                                             | I <sub>LOAD</sub> = -10mA                                                                                                                                             |           |   | -15   |                        | 0                       | mV                |

|                   | BYP1 Undervoltage Lockout Threshold                                    |                                                                                                                                                                       |           |   |       |                        | 2.25                    | V                 |

| V <sub>BYP2</sub> | BYP2 Regulation Output Voltage                                         |                                                                                                                                                                       |           |   | 3     | 3.25                   | 3.6                     | V                 |

|                   | BYP2 Load Current                                                      |                                                                                                                                                                       |           |   | -10   |                        | 0                       | mA                |

|                   | BYP2 Load Regulation Error                                             | I <sub>LOAD</sub> = -10mA                                                                                                                                             |           |   | -60   |                        |                         | mV                |

|                   | Thermal Shutdown Temperature                                           |                                                                                                                                                                       |           |   |       | 170                    |                         | °C                |

| Current Se        | nse ADC                                                                | 1                                                                                                                                                                     |           |   |       |                        | I                       |                   |

|                   | Resolution (No Missing Codes)                                          | Slow Mode Filtered (No                                                                                                                                                | te 7)     |   | 20    |                        |                         | Bit               |

|                   |                                                                        | Slow Mode (Note 7)                                                                                                                                                    |           |   | 18    |                        |                         | Bit               |

|                   |                                                                        | Fast Mode (Note 7)                                                                                                                                                    |           |   | 15    |                        |                         | Bit               |

|                   | Full-Scale Differential Input Voltage                                  | V <sub>I1P</sub> -V <sub>I1M</sub> , V <sub>I2P</sub> -V <sub>I2M</sub>                                                                                               |           |   |       | ±124                   |                         | mV                |

| VDIFI             | Differential Input Voltage Range                                       | V <sub>I1P</sub> -V <sub>I1M</sub> , V <sub>I2P</sub> -V <sub>I2M</sub>                                                                                               |           |   |       |                        | ±110                    | mV                |

|                   | Pin Voltage of I1P, I1M, I2P, I2M                                      |                                                                                                                                                                       |           |   | -0.11 |                        | V <sub>AVCC</sub> +0.11 | V                 |

|                   | Current Sense Quantization Step                                        | Slow Mode Filtered                                                                                                                                                    |           |   |       | 237.5                  |                         | nV                |

|                   |                                                                        | Slow Mode                                                                                                                                                             |           |   |       | 950                    |                         | nV                |

|                   |                                                                        | Fast Mode                                                                                                                                                             |           |   |       | 7.60371                |                         | μV                |

| CFPx              | Input Leakage Current at CF1P, CF1M, I1P,<br>I1M, CF2P, CF2M, I2P, I2M | Core State = SLEEP/ST/                                                                                                                                                | ANDBY     | • |       |                        | <mark>40</mark><br>60   | nA                |

|                   | Differential Input Current from CF1P to CF1M,<br>CF2P to CF2M          | Core State: MEASURE; P<br>V <sub>CF1P</sub> , V <sub>CF1M</sub> , V <sub>I1P</sub> , V <sub>I1N</sub><br>V <sub>I2P</sub> , V <sub>I2M</sub> $\leq$ V <sub>AVCC</sub> |           |   | ١     | VDIF <sub>I</sub> /100 | kΩ                      | μA                |

|                   | Noise                                                                  | Slow Mode Filtered                                                                                                                                                    |           |   |       | 160                    |                         | nV <sub>RMS</sub> |

|                   |                                                                        | Slow Mode                                                                                                                                                             |           |   |       | 320                    |                         | nV <sub>RMS</sub> |

|                   |                                                                        | Fast Mode                                                                                                                                                             |           |   |       | 3                      |                         | μV <sub>RMS</sub> |

|                   | Gain Error                                                             | $ VDIF_{I}  \le 110mV$                                                                                                                                                |           |   |       |                        | 0.15                    | %                 |

|                   |                                                                        |                                                                                                                                                                       |           |   |       |                        | 0.3                     | %                 |

|                   | Offset Voltage                                                         | IADCx, IxP, IxM = 0V                                                                                                                                                  | Slow Mode |   |       | 0                      | ±1                      | μV                |

|                   |                                                                        | $V_{AVCC} = V_{DVCC} = 5V$                                                                                                                                            | Fast Mode |   |       | 0                      | ±2                      | μV                |

|                   | Total Unadjusted Error                                                 | $ VDIF_1  \ge 25mV$                                                                                                                                                   |           |   |       |                        | 0.3                     | %                 |

| SYMBOL           | PARAMETER                                    | CONDITIONS                                                                                    |   | MIN  | ТҮР      | MAX                    | UNITS               |

|------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------|---|------|----------|------------------------|---------------------|

|                  | Input Voltage Common Mode Rejection at DC    |                                                                                               |   | 100  |          |                        | dB                  |

|                  | Input Sampling Frequency                     |                                                                                               |   |      | 10.48    |                        | MHz                 |

|                  | Conversion Time                              | Slow Mode Filtered                                                                            |   |      | 400      |                        | ms                  |

|                  |                                              | Slow Mode                                                                                     |   |      | 100      |                        | ms                  |

|                  |                                              | Fast Mode                                                                                     |   |      | 0.782    | 0.8211                 | ms                  |

| Voltage Me       | easurement by Power ADC                      |                                                                                               |   |      |          |                        |                     |

|                  | Resolution (No Missing Codes)                | Slow Mode (Note 7)                                                                            |   | 18   |          |                        | Bit                 |

|                  |                                              | Fast Mode (Note 7)                                                                            |   | 15   |          |                        | Bit                 |

| VFSV             | Full-Scale Differential Input Voltage        | V <sub>VBATP</sub> – V <sub>VBATM</sub>                                                       |   |      | ±6.14    |                        | V                   |

| VDIFV            | Differential Input Voltage Range             | V <sub>VBATP</sub> – V <sub>VBATM</sub>                                                       |   |      |          | ±4.8                   | V                   |

|                  | Pin Voltage of VBATP, VBATM                  | $V_{AVCC} \ge 5V$                                                                             |   | -0.1 |          | V <sub>AVCC</sub> +0.1 | V                   |

|                  |                                              | V <sub>AVCC</sub> < 5V                                                                        |   | -0.1 |          | V <sub>AVCC</sub> -1.5 | V                   |

| LSBV             | Differential Input Voltage Quantization Step | Slow Mode                                                                                     |   |      | 46.875   |                        | μV                  |

|                  |                                              | Fast Mode                                                                                     |   |      | 375.183  |                        | μV                  |

|                  | Input Leakage Current                        | Core State: SLEEP/STANDBY                                                                     |   |      |          | 10                     | 60 nA               |

|                  | Differential Input Resistance                | Core State: MEASURE; Pin Voltages 0V                                                          |   | 50   |          |                        | MΩ                  |

|                  |                                              | $\leq$ V <sub>BATP</sub> , V <sub>BATM</sub> $\leq$ V <sub>AVCC</sub>                         |   | 20   |          |                        | MΩ                  |

|                  | Gain Error                                   |                                                                                               |   |      |          | 0.3                    | %                   |

|                  | Offset                                       | V <sub>BATP</sub> = V <sub>BATM</sub> = 0V                                                    |   |      | 0        | ±3                     | LSBV                |

|                  | Voltage Total Unadjusted Error               | $1V \le  VDIF_V  \le 4.8V$                                                                    |   |      |          | 0.4                    | %                   |

|                  | Input Voltage Common Mode Rejection at DC    |                                                                                               |   | 80   |          |                        | dB                  |

|                  | Noise                                        | Slow Mode (Note 7)                                                                            |   |      | 3        |                        | μV <sub>RMS</sub>   |

|                  |                                              | Fast Mode (Note 7)                                                                            |   |      | 30       |                        | μV <sub>RMS</sub>   |

|                  | Input Sampling Rate                          |                                                                                               |   |      | 5.24     |                        | MHz                 |

|                  | Conversion Time                              | Slow Mode                                                                                     |   |      | 100      |                        | ms                  |

|                  |                                              | Fast Mode                                                                                     |   |      | 0.782    | 0.8211                 | ms                  |

| Power Mea        | asurement by Power ADC                       |                                                                                               |   |      |          |                        |                     |

|                  | Resolution (No Missing Codes)                | Slow Mode (Note 7)                                                                            |   | 18   |          |                        | Bit                 |

|                  |                                              | Fast Mode (Note 7)                                                                            |   | 11   |          |                        | Bit                 |

| FS <sub>P</sub>  | Full-Scale Power                             | $FS_P = VFS_V \bullet VFS_I/R_{ISENSE}/VDIV_V$                                                |   |      | ±0.76504 |                        | [V <sup>2</sup> /Ω] |

| LSB <sub>P</sub> | Power Quantization Step                      | $LSB_{P} = FS_{P}/2^{17}$                                                                     |   |      | 5.8368   |                        | $\mu[V^2/\Omega]$   |

| POS              | Power Offset                                 | VDIF <sub>1</sub> = 0                                                                         |   |      | 1        |                        | LSB <sub>P</sub>    |

| TUE <sub>P</sub> | Power Total Unadjusted Error                 | $\begin{array}{l} 1V \leq  VDIF_V  \leq 4.8V, \ 25mV \leq  VDIF_I  \leq \\ 110mV \end{array}$ | • |      |          | 0.9                    | %                   |

|                  | RMS Noise                                    | Slow Mode; VBATP – VBATM = 4.8V (Note 7)                                                      |   |      | 0.3      |                        | LSBP                |

|                  |                                              | Slow Mode; VBATP – VBATM = 0V (Note 7)                                                        |   |      | 0.03     |                        | LSBP                |

|                  | Input Sampling Frequency                     |                                                                                               |   |      | 5.24     |                        | MHz                 |

|                  | Power Modulation Frequency                   |                                                                                               |   |      | 5.24     |                        | MHz                 |

|                  | Conversion Time                              | Slow Mode                                                                                     |   |      | 100      |                        | ms                  |

|                  |                                              | Fast Mode                                                                                     |   |      | 0.782    | 0.8211                 | ms                  |

5

| SYMBOL              | PARAMETER                                    | CONDITIONS                                                                                                                                       |     | MIN  | ТҮР     | MAX                    | UN | IITS |

|---------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------|------------------------|----|------|

| Energy Me           | asurement                                    | 1                                                                                                                                                | 1   |      |         | -                      | 1  |      |

| TUE <sub>E</sub>    | Energy Total Unadjusted Error                | $\begin{array}{ l l l l l l l l l l l l l l l l l l l$                                                                                           | •   |      |         | 0.9                    |    | %    |

| _                   |                                              | $\begin{array}{l} 1V \leq  VDIF_V  \leq 4.8V, \ 25mV \leq  VDIF_I  \leq \\ 110mV, \ Internal \ Clock \end{array}$                                | •   |      |         | 1.9                    |    | %    |

| Charge Me           | easurement                                   |                                                                                                                                                  |     |      |         |                        |    |      |

| TUE <sub>C</sub>    | Charge Total Unadjusted Error                | $\begin{array}{l} 1V \leq  VDIF_V  \leq 4.8V, \ 25mV \leq  VDIF_I  \leq \\ 110mV, \ Ideal \ External \ Clock \ or \ 4MHz \\ Crystal \end{array}$ | •   |      |         | 0.4                    |    | %    |

|                     |                                              | $\begin{array}{l} 1V \leq  VDIF_V  \leq 4.8V, \ 25mV \leq  VDIF_I  \leq \\ 110mV, \ Internal \ Clock \end{array}$                                | •   |      |         | 1.4                    |    | %    |

| Voltage Me          | easurement by AUXILIARY ADC                  | ·                                                                                                                                                |     |      |         |                        |    |      |

|                     | Resolution (No Missing Codes)                | (Note 7)                                                                                                                                         |     | 15   |         |                        |    | Bit  |

| VFS <sub>AUX</sub>  | Full-Scale Differential Input Voltage        | V <sub>VBATP</sub> – V <sub>VBATM</sub> , V <sub>MUXP</sub> – V <sub>MUXN</sub>                                                                  |     |      | ±6.14   |                        |    | V    |

| VDIF <sub>AUX</sub> | Differential Input Voltage Range             | V <sub>VBATP</sub> – V <sub>VBATM</sub> , V <sub>MUXP</sub> – V <sub>MUXN</sub>                                                                  | •   |      |         | ±4.8                   |    | V    |

|                     | Pin Voltage of VBATP, VBATM, V1 – V12, CF1P, | $V_{AVCC} \ge 5V$                                                                                                                                |     | -0.1 |         | V <sub>AVCC</sub> +0.1 |    | V    |

|                     | CF1M, CF2P, CF2M                             | V <sub>AVCC</sub> < 5V                                                                                                                           | •   | -0.1 |         | V <sub>AVCC</sub> -1.5 |    | V    |

| LSB <sub>AUX</sub>  | Differential Voltage Quantization Step       | Slow Mode                                                                                                                                        |     |      | 375     |                        |    | μV   |

|                     |                                              | Fast Mode                                                                                                                                        |     |      | 375.183 |                        |    | μV   |

|                     | Input Leakage Current                        |                                                                                                                                                  |     |      | 1       | 10                     | 60 | nA   |

|                     | Differential Input Resistance                |                                                                                                                                                  |     | 40   |         |                        |    | MΩ   |

|                     | Gain Error                                   | $ VDIF_{AUX}  \le 4.8V$                                                                                                                          |     |      |         | 0.3                    |    | %    |

|                     | Offset                                       | $V_{BATP} = V_{BATM} = 0V$                                                                                                                       |     |      | 0       | ±1                     | L  | SBV  |

|                     | Total Unadjusted Error                       | $1V \le  VDIF_V  \le 4.8V$                                                                                                                       | •   |      |         | 0.4                    |    | %    |

|                     | Input Voltage Common Mode Rejection at DC    |                                                                                                                                                  |     | 80   |         |                        |    | dB   |

|                     | Sampling Rate                                |                                                                                                                                                  |     |      | 5.24    |                        | ſ  | MHz  |

|                     | Conversion Time                              |                                                                                                                                                  |     |      | 0.782   | 0.8211                 |    | ms   |

| On-Die Ter          | nperature Measurement by AUXILIARY ADC       |                                                                                                                                                  |     |      |         |                        |    |      |

|                     | Resolution (No Missing Codes)                | (Note 7)                                                                                                                                         |     | 13   |         |                        |    | Bit  |

|                     | Full-Scale Temperature                       |                                                                                                                                                  |     |      | 819.2   |                        |    | K    |

| $\Delta T_{LSB}$    | Temperature Quantization Step                |                                                                                                                                                  |     |      | 0.2     |                        |    | K    |

|                     | Total Unadjusted Error                       |                                                                                                                                                  |     |      | ±3      |                        |    | K    |

|                     | Conversion Time                              |                                                                                                                                                  |     |      | 13.1    |                        |    | ms   |

|                     | Self-Heating                                 |                                                                                                                                                  |     |      | 20      |                        |    | K/W  |

| Supply Vol          | tage Measurement by AUXILIARY ADC            |                                                                                                                                                  |     |      |         |                        |    |      |

|                     | Resolution (No Missing Codes)                | (Note 7)                                                                                                                                         |     | 14   |         |                        |    | Bit  |

|                     | Full-Scale Differential Input Voltage        |                                                                                                                                                  |     |      | 18.43   |                        |    | V    |

|                     | A/DVCC Measurement Quantization Step         |                                                                                                                                                  |     |      | 2.2583  |                        |    | mV   |

|                     | Total Unadjusted Error                       |                                                                                                                                                  |     |      | 2       | ±5                     |    | %    |

|                     | Conversion Time                              |                                                                                                                                                  |     |      | 6.55    |                        |    | ms   |

| AUX MUX             |                                              | 1                                                                                                                                                | _,, |      |         |                        |    |      |

|                     | Signal Range                                 |                                                                                                                                                  |     | -0.1 |         | V <sub>AVCC</sub> +0.1 |    | V    |

Rev A

| SYMBOL           | PARAMETER                                    | CONDITIONS                                                                                 |   | MIN                         | ТҮР  | MAX                         | UNITS                                        |

|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|---|-----------------------------|------|-----------------------------|----------------------------------------------|

|                  | Pull-Up Current Source                       | Pin Voltage < V <sub>AVCC</sub> – 3.0V                                                     |   |                             | -250 | -150                        | μA                                           |

|                  | Pull-Down Current Source                     | Pin Voltage > 2.5V                                                                         | • | 200                         | 250  |                             | μΑ                                           |

| Reference        | Voltages                                     |                                                                                            |   | 1                           |      |                             | <u>.                                    </u> |

| VREF             | Reference Pin Voltage                        |                                                                                            |   |                             | 3    |                             | V                                            |

|                  | VREF Error                                   |                                                                                            | • |                             |      | ±1                          | %                                            |

|                  | VREF Temperature Coefficient                 |                                                                                            |   |                             | 7    |                             | ppm/k                                        |

|                  | VREF Long Term Drift                         |                                                                                            |   |                             | 80   |                             | ppm/√kHr                                     |

|                  | VREF Load Regulation Error                   | $-0.5$ mA $\leq I_{LOAD} \leq 0.5$ mA                                                      | • | -5                          |      | 0                           | m۱                                           |

| VREF2            | Internal Redundant Reference Voltage         |                                                                                            |   |                             | 2.39 |                             | \<br>\                                       |

|                  | VREF2 Error                                  |                                                                                            | • |                             |      | ±0.85                       | %                                            |

|                  | VREF2 Temperature Coefficient                |                                                                                            |   |                             | 10   |                             | ppm/k                                        |

|                  | VREF2 Long Term Drift                        |                                                                                            |   |                             | 80   |                             | ppm/√kHr                                     |

| Overcurren       | nt Comparator                                |                                                                                            |   |                             |      |                             |                                              |

|                  | Pin Voltages I1P, I1M I2P, I2M               |                                                                                            |   | -0.11                       |      | V <sub>AVCC</sub> +0.11     | V                                            |

|                  | Total Unadjusted Error                       | Vthr  ≤ 103mV                                                                              | • |                             |      | ±5                          | m۷                                           |

|                  |                                              | Vthr  > 103mV                                                                              | • |                             |      | ±10                         | m\                                           |

|                  |                                              | Vthr  = 310mV                                                                              | • |                             |      | ±20                         | m\                                           |

|                  | Programmable Deglitch Time Delay             | T <sub>degl</sub> 20, 80, 320µs                                                            | • | T <sub>degl</sub> -10       |      | T <sub>degl</sub> +37       | μ                                            |

|                  |                                              | T <sub>degl</sub> 1280μs                                                                   | • | T <sub>degl</sub> -26       |      | T <sub>degl</sub> +56       | με                                           |

| Digital Inp      | ut CLKI                                      |                                                                                            |   | ·                           |      |                             |                                              |

|                  | Logic Input Threshold                        |                                                                                            | • | 0.4                         |      | 2                           | \<br>\                                       |

|                  | Input Current DC Current                     |                                                                                            | • |                             |      | ±1                          | μA                                           |

|                  | Input Capacitance                            | (Note 7)                                                                                   | • |                             |      | 10                          | pF                                           |

|                  | External Clock Frequency                     |                                                                                            | • | 0.1                         |      | 25                          | MHz                                          |

| General Pu       | urpose Outputs GPIOx                         |                                                                                            |   | ·                           |      |                             |                                              |

|                  | Low Level Output Voltage at GPIOx            | I <sub>GPIOx</sub> = 0.5mA                                                                 | • |                             |      | 0.4                         | V                                            |

|                  | High Level Output Voltage at GPIOx           | I <sub>GPIOx</sub> = -0.25mA                                                               | • | V <sub>DVCC</sub><br>-0.5   |      |                             | V                                            |

|                  | GPIOx Toggling Frequency                     |                                                                                            | • | 370                         | 400  | 430                         | kHz                                          |

| SPI Interfa      | ce DC Specification IOVCC, CSB, SCK, SDI, SI | DO                                                                                         |   |                             |      |                             |                                              |

| VIOVCC           | SPI Mode IOVCC Operating Voltage             |                                                                                            |   | 1.8                         |      | 4.5                         | V                                            |

|                  | Pin Voltages CSB, SCK, SDI, SDO              |                                                                                            |   |                             |      | VIOVCC                      | \<br>\                                       |

|                  | Logic Input Threshold (CSB, SCK, SDI)        |                                                                                            | • | 0.3 •<br>V <sub>IOVCC</sub> |      | 0.7 •<br>V <sub>IOVCC</sub> | \<br>\                                       |

|                  | DC Input Current (CSB, SCK, SDI)             |                                                                                            | • |                             |      | ±1                          | μΑ                                           |

|                  | Input Capacitance (CSB, SCK, SDI)            | (Note 7)                                                                                   | • |                             |      | 10                          | pl                                           |

|                  | Low Level Output Voltage at SDO              | $V_{10VCC} \geq 3.3V, \; I_{SDO}$ = 3mA, $1.8V \leq V_{10VCC} \leq 3.3V, \; I_{SDO}$ = 1mA | • |                             |      | 0.4                         | \                                            |

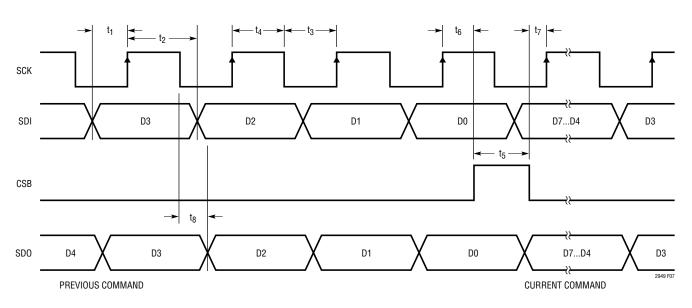

| SPI Timing       | Requirements (See Figure 7)                  |                                                                                            |   |                             |      |                             |                                              |

| t <sub>CLK</sub> | SCK Period                                   | (Note 6)                                                                                   | • | 1                           |      |                             | μ                                            |

| t <sub>1</sub>   | SDI Setup Time Before SCK Rising Edge        |                                                                                            |   | 25                          |      |                             | n                                            |

| t <sub>2</sub>   | SDI Hold Time After SCK Rising Edge          |                                                                                            |   | 25                          |      |                             | ns                                           |

| SYMBOL                | PARAMETER                                             | CONDITIONS                                                                |   | MIN  | ТҮР                                                    | MAX  | UNITS |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------------------|---|------|--------------------------------------------------------|------|-------|

| t <sub>3</sub>        | SCK Low                                               | $t_{CLK} = t_3 + t_4 \ge 1 \mu s$                                         |   | 200  |                                                        |      | ns    |

| t <sub>4</sub>        | SCK High                                              | $t_{CLK} = t_3 + t_4 \ge 1 \mu s$                                         | • | 200  |                                                        |      | ns    |

| t <sub>5</sub>        | CSB Rising Edge to CSB Falling Edge                   |                                                                           | • | 0.65 |                                                        |      | μs    |

| t <sub>6</sub>        | SCK Rising Edge to CSB Rising Edge                    | (Note 6)                                                                  | • | 0.8  |                                                        |      | μs    |

| t <sub>7</sub>        | CSB Falling Edge to SCK Rising Edge                   | (Note 6)                                                                  |   | 1    |                                                        |      | μs    |

| t <sub>8</sub>        | SCK Falling Edge to SDO Valid                         | (Note 9), VIOVCC ≥ 3.3V                                                   | • |      |                                                        | 60   | ns    |

|                       |                                                       | (Note 9), VIOVCC < 3.3V                                                   |   |      |                                                        | 150  | ns    |

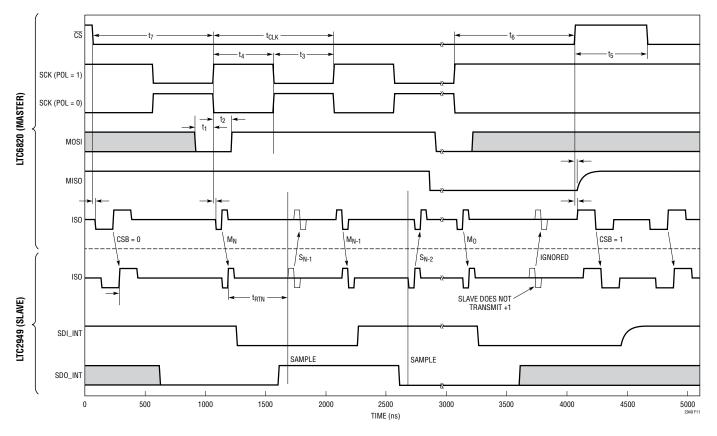

| isoSPI DC             | Specifications (See Figure 10)                        |                                                                           |   |      |                                                        |      |       |

|                       | Voltage at IOVCC to Select isoSPI                     |                                                                           |   |      |                                                        | 0.5  | V     |

| V <sub>IBIAS</sub>    | Voltage on IBIAS Pin                                  | READY/ACTIVE State                                                        | • | 1.9  | 2                                                      | 2.1  | V     |

|                       |                                                       | IDLE                                                                      |   |      | 0                                                      |      | V     |

| I <sub>B</sub>        | Isolated Interface Bias Current                       | $R_{BIAS} = 2k\Omega$ to $20k\Omega$                                      |   | 0.1  |                                                        | 1    | mA    |

| A <sub>IB</sub>       | Isolated Interface Current Gain                       | $V_A \le 1V, I_B = 1mA$                                                   | • | 18   | 20                                                     | 22   | mA/mA |

|                       |                                                       | I <sub>B</sub> = 0.1mA                                                    |   | 17   | 20                                                     | 24.5 | mA/mA |

| V <sub>A</sub>        | Transmitter Pulse Amplitude                           | $V_A =  V_{IP} - V_{IM} $                                                 | • |      |                                                        | 1.4  | V     |

| VICMP                 | Threshold-Setting Voltage on ICMP Pin                 | $V_{\text{TCMP}} = A_{\text{TCMP}} \bullet V_{\text{ICMP}}$               |   | 0.2  |                                                        | 1.5  | V     |

|                       | Input Leakage Current on ICMP Pin                     | $V_{ICMP} = 0V \text{ to } V_{BYP2}$                                      | • |      |                                                        | ±1   | μA    |

|                       | Leakage Current on IP and IM Pins                     | IDLE State, $V_{IP}$ or $V_{IM} = 0V$ to $V_{BYP2}$                       |   |      |                                                        | ±1   | μA    |

| A <sub>TCMP</sub>     | Receiver Comparator Threshold Voltage Gain            | $V_{CM} = V_{BYP2}/2$ to $V_{BYP2} - 0.2V$ ,<br>$V_{ICMP} = 0.2V$ to 1.5V | • | 0.4  | 0.5                                                    | 0.6  | V/V   |

| V <sub>CM</sub>       | Receiver Common Mode Bias                             | IP, IM Not Driving                                                        |   |      | V <sub>BYP2</sub> –<br>V <sub>ICMP</sub> /3 –<br>167mV |      | V     |

|                       | Receiver Input Resistance                             | Single-Ended to IP, IM                                                    |   | 27   | 35                                                     | 43   | kΩ    |

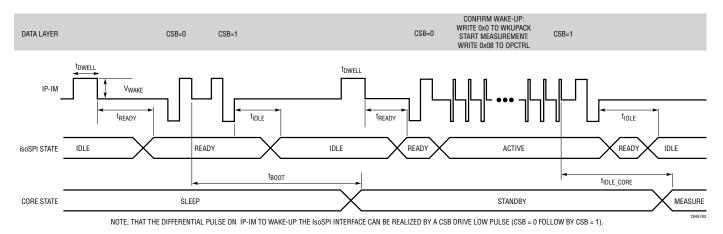

| isoSPI IDLI           | E/WAKE-UP Specifications (See Figure 3)               |                                                                           |   |      |                                                        |      |       |

| V <sub>WAKE</sub>     | Differential Wake-Up Voltage                          | t <sub>DWELL</sub> = 240ns                                                |   | 200  |                                                        |      | mV    |

| t <sub>DWELL</sub>    | Dwell Time at V <sub>WAKE</sub> Before Wake Detection | V <sub>WAKE</sub> = 200mV                                                 | • | 240  |                                                        |      | ns    |

| t <sub>READY</sub>    | Start-Up Time After Wake Detection                    |                                                                           |   |      |                                                        | 10   | μs    |

| t <sub>IDLE</sub>     | Idle Timeout Duration                                 |                                                                           | • | 4.3  | 6.4                                                    | 8    | ms    |

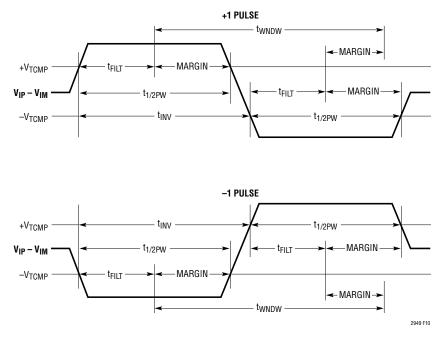

|                       | se Timing Specifications (See Figures 10,11)          |                                                                           |   |      |                                                        |      |       |

| t <sub>FILT(CS)</sub> | Chip-Select Signal Filter                             | Receiver                                                                  |   | 70   | 90                                                     | 115  | ns    |

| t <sub>WNDW(CS)</sub> | Chip-Select Valid Pulse Window                        | Receiver                                                                  | • | 220  | 270                                                    | 330  | ns    |

| t <sub>1/2PW(D)</sub> | Data Half-Pulse Width                                 | Transmitter                                                               | • | 40   | 50                                                     | 60   | ns    |

| t <sub>FILT(D)</sub>  | Data Signal Filter                                    | Receiver                                                                  |   | 10   | 25                                                     | 35   | ns    |

| t <sub>INV(D)</sub>   | Data Pulse Inversion Delay                            | Transmitter                                                               |   | 40   | 55                                                     | 69   | ns    |

| t <sub>WNDW(D)</sub>  | Data Valid Pulses Window                              | Receiver                                                                  | • | 70   | 90                                                     | 110  | ns    |

| t <sub>RTN</sub>      | Data Return Delay                                     |                                                                           | • |      | 485                                                    | 625  | ns    |

|                       | e DC Specification (SCL, SDA)                         |                                                                           |   |      |                                                        |      | L     |

|                       | Logic Input Threshold (SDA)                           |                                                                           |   | 0.9  |                                                        | 1.6  | V     |

|                       | DC Input Current (SDA)                                |                                                                           | • |      |                                                        | ±1   | μA    |

|                       | Input Capacitance (SDA)                               | (Note 7)                                                                  | • |      |                                                        | 10   | pF    |

|                       | Low Level Output Voltage at SDA, SCL                  | I = 0.5mA                                                                 |   |      |                                                        | 0.4  | v v   |

Rev A

| SYMBOL                     | PARAMETER                                                                         | CONDITIONS                                                         |   | MIN                          | ТҮР | MAX | UNITS |

|----------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------|---|------------------------------|-----|-----|-------|

| I <sup>2</sup> C Interface | Timing Specification (SCL, SDA)                                                   |                                                                    |   |                              |     | I   |       |

| f <sub>SCL(MAX)</sub>      | Maximum SCL Clock Frequency                                                       |                                                                    | • |                              | 8   | 10  | kHz   |

| t <sub>SCLLO</sub>         | SCL Low Period                                                                    |                                                                    | • | 80                           |     |     | μs    |

| t <sub>SDALO</sub>         | SDA Low Period                                                                    |                                                                    | • | 80                           |     |     | μs    |

| t <sub>BUF(MIN)</sub>      | Bus Free Time Between STOP/START                                                  |                                                                    | • | 30                           |     |     | μs    |

| t <sub>SU,STA(MIN)</sub>   | Minimum Repeated START Setup Time                                                 |                                                                    | • | 30                           |     |     | μs    |

| t <sub>hd,sta(min)</sub>   | Minimum Hold Time (Repeated) START<br>Condition                                   |                                                                    | • | 30                           |     |     | μs    |

| t <sub>SU,STO(MIN)</sub>   | Minimum Setup Time for STOP Condition                                             |                                                                    | • | 30                           |     |     | μs    |

| t <sub>SU,DAT(MIN)</sub>   | Minimum Data Setup Time Input                                                     |                                                                    | • | 30                           |     |     | μs    |

| t <sub>HD,DAT(MIN)</sub>   | Minimum Data Hold Time Input                                                      |                                                                    | • |                              |     | 0   | ns    |

| t <sub>HD,DATO</sub>       | Minimum Data Hold Time Output                                                     |                                                                    | • | 30                           |     |     | μs    |

| t <sub>OF</sub>            | Data Output Fall Time                                                             | (Notes 7, 8)                                                       | • | 20 + 0.1<br>• C <sub>B</sub> |     |     | ns    |

| <b>Digital Core</b>        | Timings (See Figure 3)                                                            |                                                                    |   |                              |     |     |       |

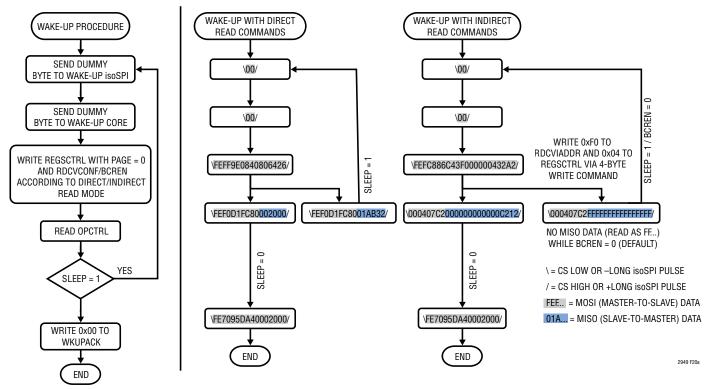

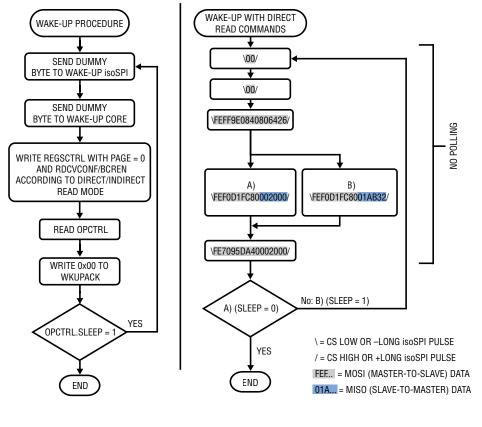

| t <sub>BOOT</sub>          | Core Boot-Up Time from SLEEP or POWER-OFF to STANDBY                              | AVCC/DVCC Pins at Minimum Operating Voltage                        | • |                              |     | 100 | ms    |

| t <sub>IDLE_CORE</sub>     | Core STANDBY Cycle Time                                                           | (Note 10)                                                          | • |                              | 17  | 20  | ms    |

| t <sub>CONT</sub>          | Core MEASURE Cycle Time                                                           | (Note 11)                                                          | • | 90                           | 100 | 110 | ms    |

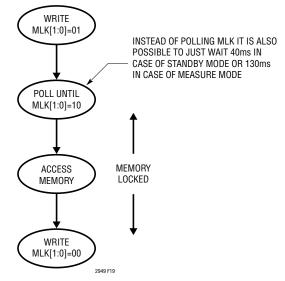

| t <sub>MLCK,M</sub>        | Memory Lock Request to Acknowledge Time                                           | Core Status MEASURE                                                | • |                              |     | 130 | ms    |

| t <sub>MLCK,S</sub>        | Memory Lock Request to Acknowledge Time                                           | Core Status STANDBY                                                | • |                              |     | 40  | ms    |

| t <sub>ACKN</sub>          | Time from Core Entering STANDBY to Return to SLEEP, When Wake-Up is not Confirmed | No Write of 0x0 to Reg. WKUPACK, No<br>Write of 0x8 to Reg. OPCTRL | • | 0.6                          |     | 1.5 | S     |

|  | П | ie | В | a | s | e |

|--|---|----|---|---|---|---|

|  |   |    |   |   |   |   |

| THIS BUCC         |               |                |   |     |   |

|-------------------|---------------|----------------|---|-----|---|

| TUE <sub>TB</sub> | TUE Time Base | Internal Clock |   | 0.5 | % |

|                   |               |                | ٠ | 1   | % |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect the device reliability and lifetime.

Note 2: Positive currents flow into pins, negative currents flow out of pins. Minimum and maximum values refer to absolute values.

Note 3: Do not apply a voltage or current source to these pins. They must be unconnected, connected to capacitive loads or connected to a crystal according to their pin description. Otherwise permanent damage may occur.

**Note 4:** Do not apply a voltage source to these pins. Overloading these pins might disrupt operation.

Note 5: Active supply current (I<sub>CC</sub>) is dependent on the amount of time that the output drivers are active on IP and IM. During those times I<sub>CC</sub> will increase by the 20 • I<sub>B</sub> drive current. For the maximum data rate 1MHz, the drivers are active approximately 5% of the time.

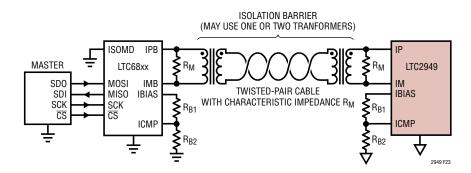

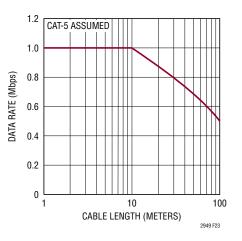

**Note 6:** These timing specifications are dependent on the delay through the cable, and include allowances for 50ns of delay each direction. 50ns corresponds to 10m of CAT-5 cable (which has a velocity of propagation of 66% the speed of light). Use of longer cables would require derating these specs by the amount of additional delay.

Note 7: Guaranteed by design and characterization, not subject to production test.

Note 8:  $C_B$  = capacitance of one bus line in pf (10pF <  $C_B$  < 400pF)

Note 9: These specifications do not include rise time of SDO due to pull up resistance and load capacitance on SDO pin.

Note 10: Cycle time at which STATUS/FAULTS and V<sub>BFF</sub> registers are updated.

Note 11: Cycle time at which STATUS/ALERT/FAULTS registers and all slow channel measurement results are updated after the first update. The first update after enabling any measurement is typically 50ms delayed.

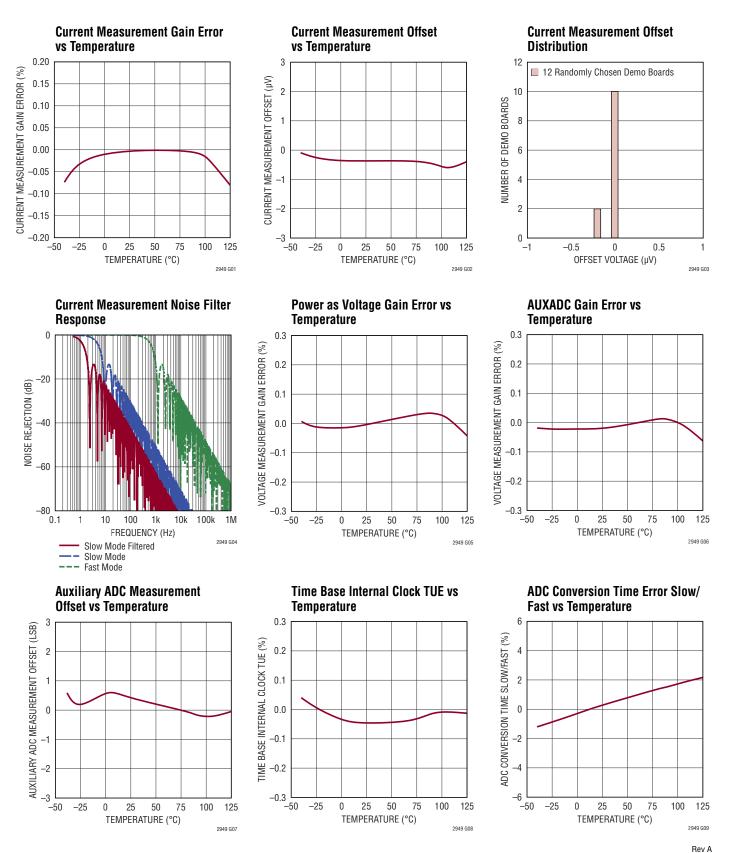

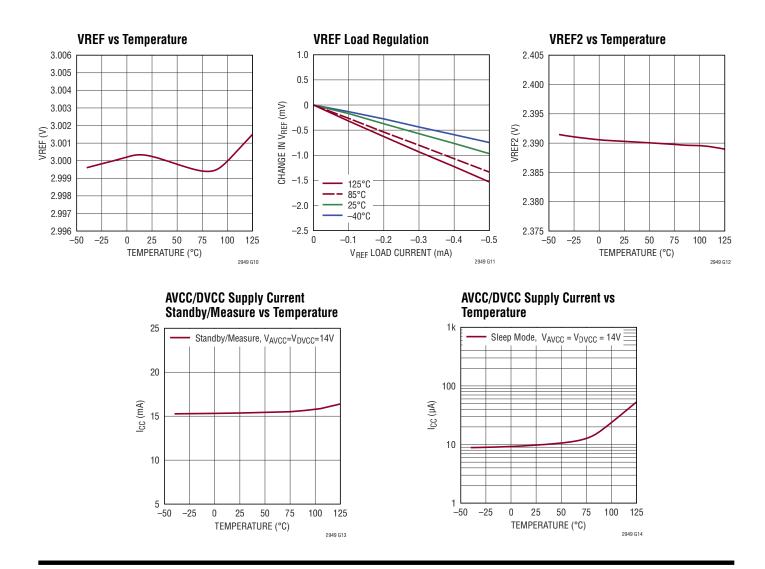

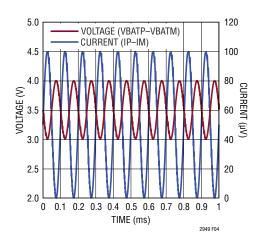

# **TYPICAL PERFORMANCE CHARACTERISTICS**

## TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

**AVCC (Pin 19):** Analog Supply Voltage. Bypass this pin to AGND with a  $0.1\mu$ F (or greater) capacitor. AVCC operating range is 4.5V to 14V.

**AGND (Pin 18):** Analog Ground. Bypass this pin to AVCC with a  $0.1\mu F$  (or greater) capacitor.

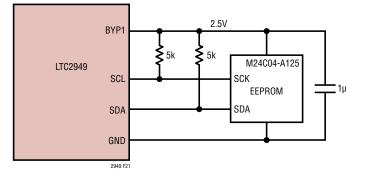

**BYP1 (Pin 16):** Internal Supply Voltage. Bypass BYP1 to DGND with a  $1\mu$ F capacitor. BYP1 is regulated to 2.5V. Can supply external circuitry (example EEPROM) with up to 10mA. Overloading might disrupt LTC2949 functionality.

**BYP2 (Pin 25):** Internal 3.25V Supply Voltage. Bypass BYP2 to DGND with a  $1\mu$ F capacitor. Can supply external circuitry (example SPI isolator ADuM141E or ADuM4154) with up to 10mA. Overloading might disrupt LTC2949 functionality.

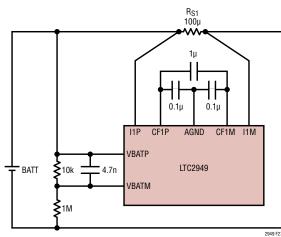

**CF1P, CF1M (Pins 44, 43):** Filter Capacitor Inputs for the first current channel. Connect a  $1\mu$ F capacitor between CF1P and CF1M for filtering differential noise and fast current variations. Connect  $0.1\mu$ F capacitors between AGND and the filter pins for damping high frequency common mode variations.

# PIN FUNCTIONS

**CF2P, CF2M (Pins 39, 40):** Filter Capacitor Inputs for the second current channel. Connect a  $1\mu$ F capacitor between CFI2P and CFI2M for filtering differential noise and fast current variations. Connect  $0.1\mu$ F capacitors between AGND and the filter pins for damping high frequency common mode variations.

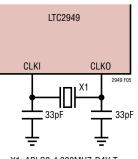

**CLKI (Pin 33):** Clock Input. Connect to ground if internal clock is used. For improved measurement accuracy, connect a 4MHz crystal between CLKI and CLKO and matching capacitors to ground, or drive with an external clock. See the Timebase Control section.

**CLKO (Pin 34):** Clock Output. Connect a 4MHz crystal between CLKO and CLKI if used; leave pin unconnected otherwise.

**CSB/IM (Pin 30):** Active Low Chip Select in SPI mode or Isolated Interface Negative Input/Output in isoSPI mode.

DGND (Pin 17): Digital Ground. Connect to AGND.

DNC (Pins 6, 21, 22, 23, 24, 31, 32, 36, 37, 46): Do not connect.

**DVCC (Pin 20):** Supply Voltage. Bypass this pin to DGND with a  $1\mu$ F capacitor. Operating range is 4.5V to 14V.

**I1P, I1M (Pins 45, 42):** Differential Input of I1ADC and overcurrent comparator 1. Tie to AGND if unused.

**12P, 12M (Pins 38, 41):** Differential Input of I2ADC and overcurrent comparator 2. Tie to AGND if unused.

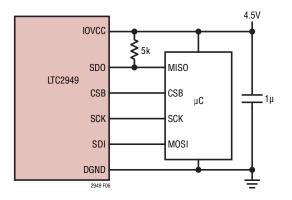

**IOVCC (Pin 26):** Serial Interface Configuration and Supply Pin. Tie pin to DGND for isoSPI communication. Tie pin to a voltage  $\geq$ 1.8V and  $\leq$  4.5V and bypass with 1µF to DGND for standard SPI communication. In SPI mode IOVCC supplies the digital input and output circuits of the serial interface.

**SCK/IP (Pin 29):** Serial Clock Input in SPI mode or Isolated Interface Positive Input/Output in isoSPI mode.

**SCL (Pin 14):** I<sup>2</sup>C Master Clock Open Drain Output. Connect to clock input of EEPROM.

**SDA (Pin 15):** I<sup>2</sup>C Data Input And Open Drain Output. Connect to data line of EEPROM. SDA driven low at power up

prevents LTC2949 to go automatically into SLEEP state and to execute HW memory BIST. Connect a 4.7k-10k pull-up resistor from SDA to BYP1 to ensure correct operation of auto-sleep and memory BIST.

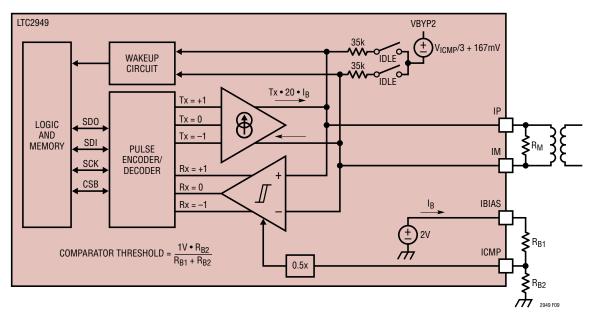

**SDI/ICMP (Pin 27):** Serial Data Input in SPI mode or Isolated Interface Comparator Voltage Threshold in isoSPI mode. Tie ICMP to the resistor divider between IBIAS and DGND to set the voltage threshold of the isoSPI receiver comparators. The comparator thresholds are set to 1/2 the voltage on the ICMP pin.

**SDO/I<sub>BIAS</sub> (Pin 28):** Open Drain Serial Data Output in SPI mode or Isolated Interface Current Bias in isoSPI mode. In SPI mode tie with a pullup resistor to IOVCC. In isoSPI mode tie IBIAS to DGND through a resistor divider to set the interface output current level. When the isoSPI interface is enabled, the IBIAS pin voltage is regulated to 2V. The IP/IM output current drive is set to 20 times the current IB, sourced from the IBIAS pin.

**V1**, **V2**, **V3**, **V4**, **V5**, **V6**, **V7** (**Pins 1**, **2**, **3**, **4**, **5**, **7**, **8**): Voltage Measurement Inputs. Pins are internally buffered before being applied to the AUXADC for ensuring high input impedance ( $50M\Omega$ ) and low leakage. Can be left floating if unused.

**V8-V12/GPI01-GPI05 (Pins 9, 10, 11, 12, 13):** General Purpose Voltage In– and Digital Outputs. Pins are internally buffered before being applied to the AUXADC for ensuring high input impedance ( $50M\Omega$ ) and low leakage (<10nA). Each pin can be switched to DVCC, switched to DGND or to toggle at 400kHz (typ.) between DVCC and DGND. Pins are tri-state in sleep mode. Can be left floating if unused.

**VBATP**, **VBATM** (Pins 48, 47): Battery Voltage Measurement. The differential voltage between VBATP and VBATM is internally buffered for ensuring high input impedance  $(50M\Omega)$  and low leakage (<10nA).

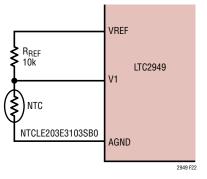

**VREF (Pin 35):** Reference Voltage Output. VREF provides a buffered 3V reference voltage for temperature measurements with NTCs. Current load is limited to 0.5mA. Bypass this pin to AGND with a  $1\mu$ F capacitor.

EXPOSED PAD (Pin 49): Connect to AGND.

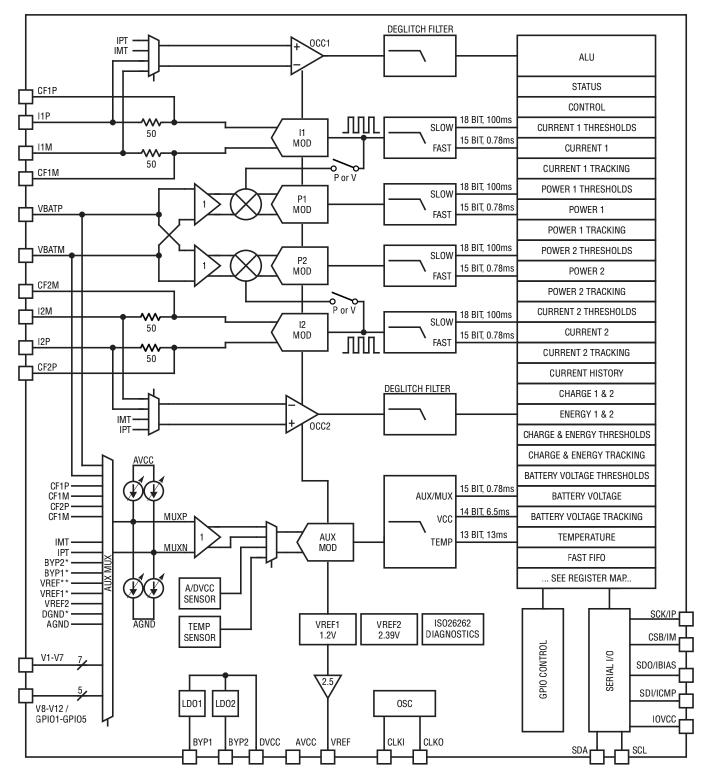

### **BLOCK DIAGRAM**

\* Measured value not accessible by user. Only used for internal diagnostics. \*\* VREF measurement value is only accessible by user from the AUX slow channel.

See also section 'Unused Input Pins V1-V12' for recommendation to allow VREF measurement from AUX fast channel.

See also 'Table 57. MUX Settings' for more details on AUX MUX configuration.

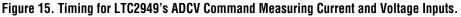

### **OVERVIEW**